La mémoire à tores.

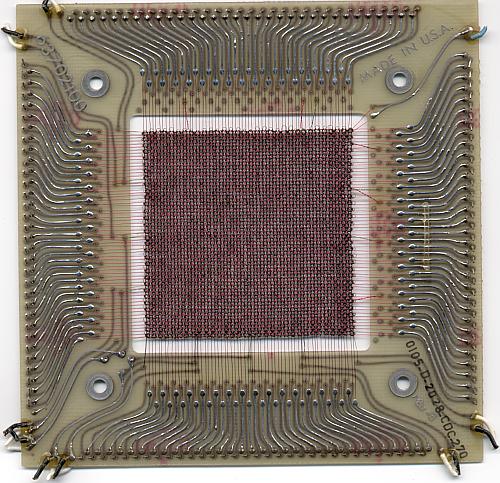

| Je me suis fait refiler dernièrement une plaque de mémoire à tores de ferrite, le genre de mémoire dont on se servait avant la généralisation des puces de RAM. Le panneau fait 64 x 64 bits, soit 4096 bits, ou 512 octets. Le texte de cette page n'y rentrerait même pas... ce qui ne veut pas dire qu'on ne pouvait rien en faire : par exemple, le noyau du ColorForth tient dans seulement 400 octets. |

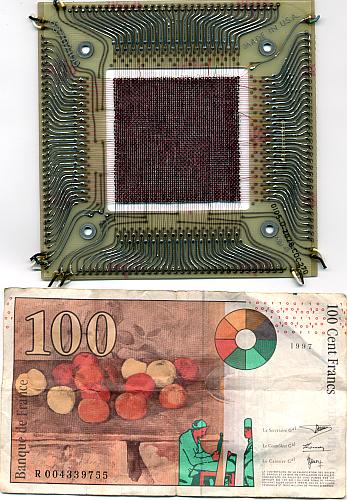

| Ce n'est pas si gros : sur cette photo, je passe la plaque au scanner, à côté d'un bout de papier sans valeur de dimensions connues. La surface couverte par les tores fait 4,8 cm de côté, ce qui donne 0,75 mm de côté par bit. |

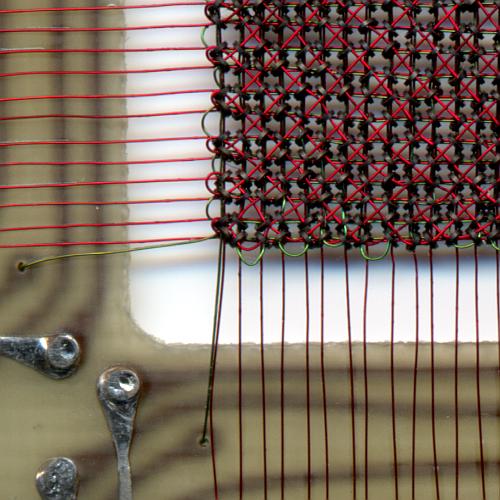

| Rapprochons-nous un peu pour en examiner la délicate structure. Cet ouvrage de tapisserie électronique était façonné à la main : s'il faut avoir de bons yeux et/ou une loupe puissante pour regarder ces détails, imaginez la difficulté des techniciens qui fabriquaient ces mémoires ; on comprend sans mal leur prix très élevé. |

| Voici une vue encore plus rapprochée, au grossissement maximal permis par mon scanner (2400 ppp)... A suivre. |